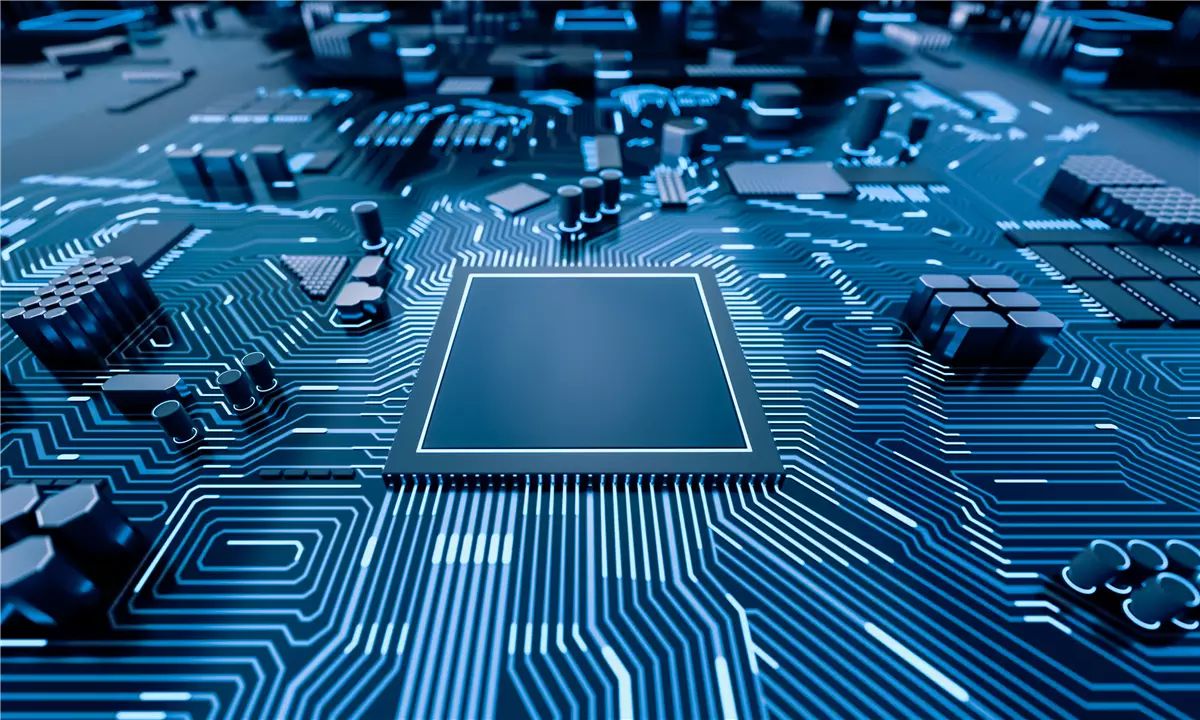

揭秘 Tensor Core 底层:如何让AI计算速度飞跃

Tensor Core,加速深度学习计算的利器,专用于高效执行深度神经网络中的矩阵乘法和卷积运算,提升计算效率。

Tensor Core凭借混合精度计算与张量核心操作,大幅加速深度学习模型的训练和推理。它采用半精度(FP16)作为输入输出,全精度(FP32)存储中间结果,确保精度同时最大化效率。这种高效计算方式,使Tensor Core能在短时间内完成大量矩阵运算,为深度学习带来质的飞跃。

Tensor Core 显著超越传统CUDA Core,每个时钟周期可执行高达4x4x4的GEMM运算,即同步完成64次浮点乘法累加(FMA),实现前所未有的计算效率。

Tensor Core的并行计算大幅加速深度学习模型的训练与推理,显著提升计算效率,引领人工智能领域迈向革命性新篇章。

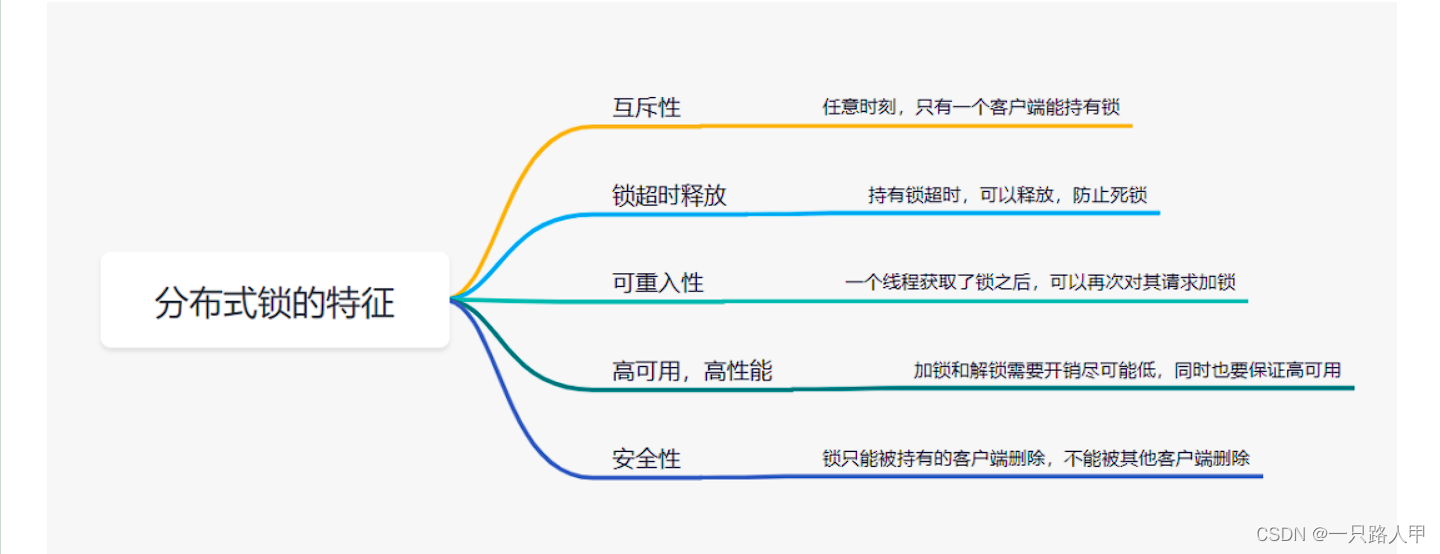

TensorCore 计算原理

下面我们首先来回顾一下 Tensor Core 的计算原理。

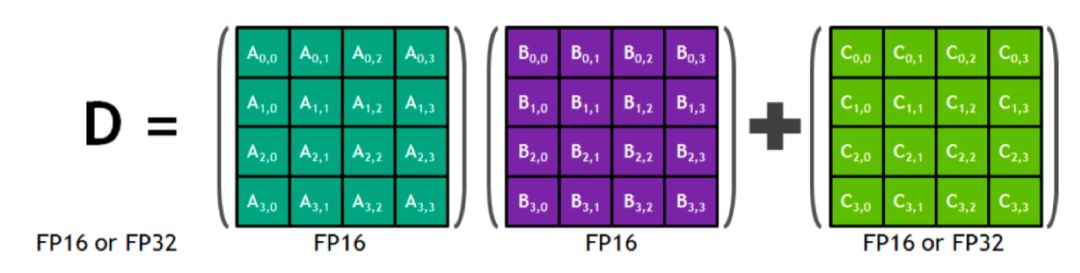

Tensor Core 计算

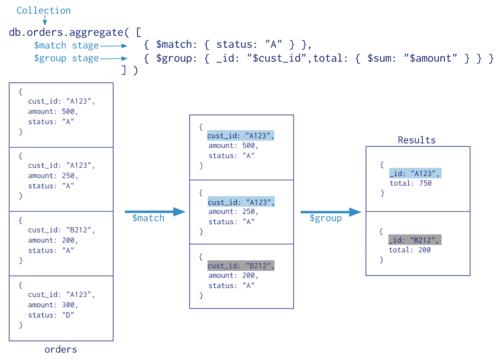

深绿色4x4矩阵A与紫色4x4矩阵B相乘,再与绿色矩阵C相加。混合精度技术在此应用中大放异彩,计算时采用FP16提高速度,而存储时则灵活选择FP32或FP16以保持数据精度,实现高效与准确性的完美融合。

数学计算中,D矩阵的元素由矩阵A的一行与矩阵B的一列相乘,再与矩阵C的对应元素相加得出,公式精准呈现这一计算过程。

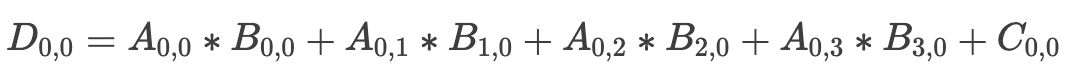

NVIDIA的GPU Tensor Core通过矩阵计算而非逐行处理,大幅提升计算效率。其计算模拟图展示了其高效能力,展现了其专业性和创新力。

Tensor Core FMA

Pascal架构(无Tensor Core)如图左,每时钟周期以元素乘行的方式,4次相乘得一列数据。而Volta架构(含Tensor Core)如图右,其Tensor Core直接计算矩阵A与B的乘积,一次性输出完整矩阵。Volta的高效性在矩阵运算中尤为显著,展现了显著的性能优势。

Volta V100 GPU相较于Pascal P100,在AI吞吐量上实现了飞跃,每个SM的AI吞吐量激增8倍。更值得一提的是,Volta架构在SM数量和核心设计上的精妙优化,使得整体性能飙升,总提升高达12倍。

TensorCore 指令流水

指令流水技术显著提升处理器效率,它将指令分解为多个精细步骤,各由专用电路并行处理。这种流水线式的连续执行方式,实现了指令的高效并行处理,极大提升了执行效率。

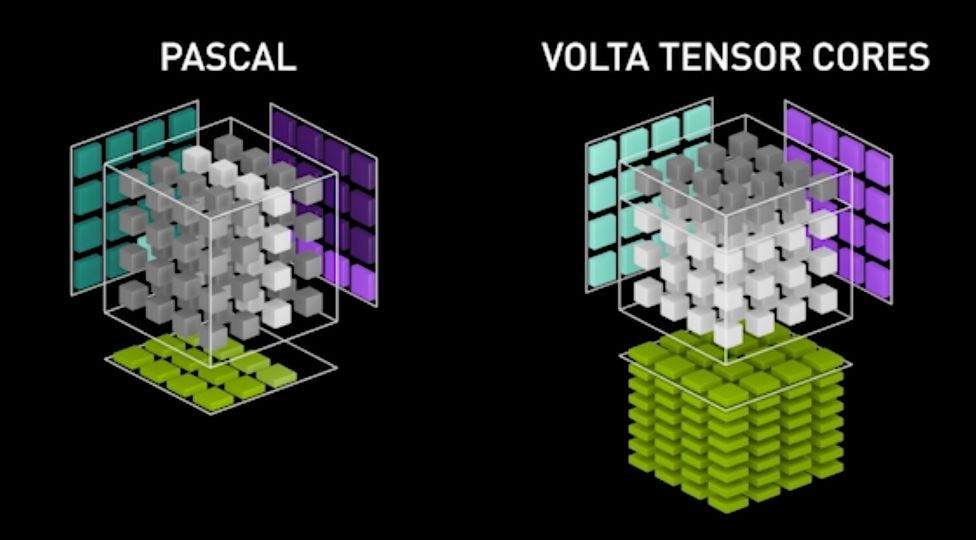

Tensor Core 模拟电路

Tensor Core模拟电路图展示了矩阵计算的核心操作。加号代表矩阵加,乘号则代表矩阵乘,这两者是矩阵计算的基础。图中绿色长方块为寄存器,其中16位横置寄存器用于存储输入与中间数据,而32位竖向寄存器则用于累积结果或高精度数据存储,确保计算高效精确。

在Tensor Core中实现矩阵相乘,即A行乘B列(假设长度均为4),其电路示意图详细展示了计算过程。无需考虑矩阵切分,我们聚焦于这一核心运算的精准实现。

Tensor Core 计算中,输入为16bit数据,乘加后需32位寄存器存储中间数据。高精度存储寄存器紧邻实际计算单元,实现A矩阵行与B矩阵列的乘法操作,简洁高效,确保计算精确性。这一设计优化了矩阵运算的效率和准确性。

GPU V100中,计算核心为矩阵间直接相乘生成新矩阵。模拟电路演示仅展示其中行列间FMA运算,生成单一元素的过程,凸显GPU强大计算能力。

那么一个矩阵中更多元素的是如何进行计算的呢?

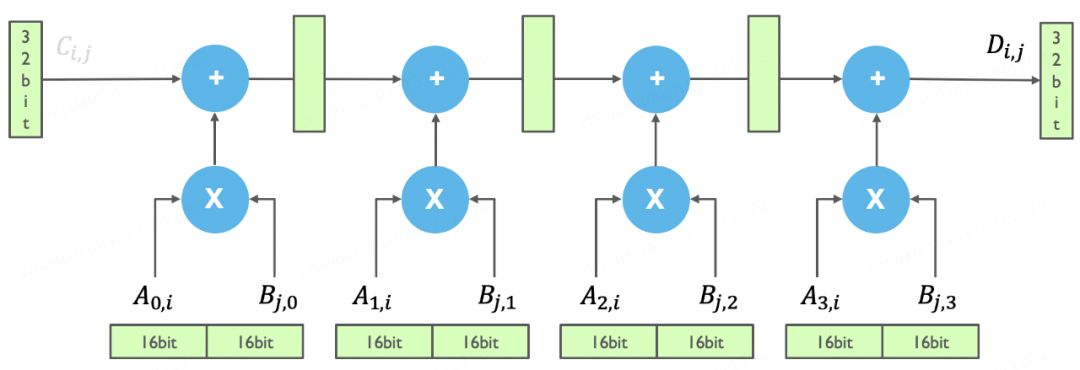

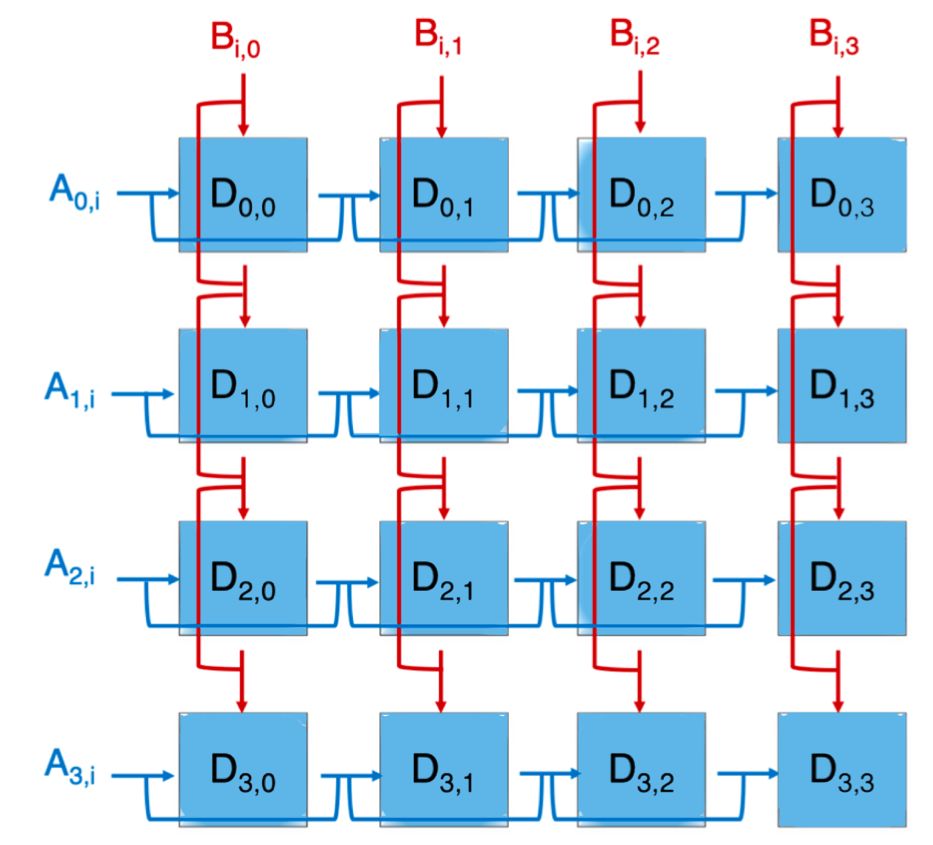

Tensor Core 矩阵模拟电路

矩阵A的行与矩阵B的列通过FMA运算生成一个元素,如首个蓝色方块所示。整体计算过程犹如电路拼接,简单地将A矩阵的每一行与B矩阵的每一列相乘,从而构建出整个矩阵的每个元素。

在此时,A、B矩阵的寄存器应各自构成一组阵列,实现并行读取与计算。这种阵列布局使矩阵的每个元素都能执行FMA计算,显著提升计算效率。

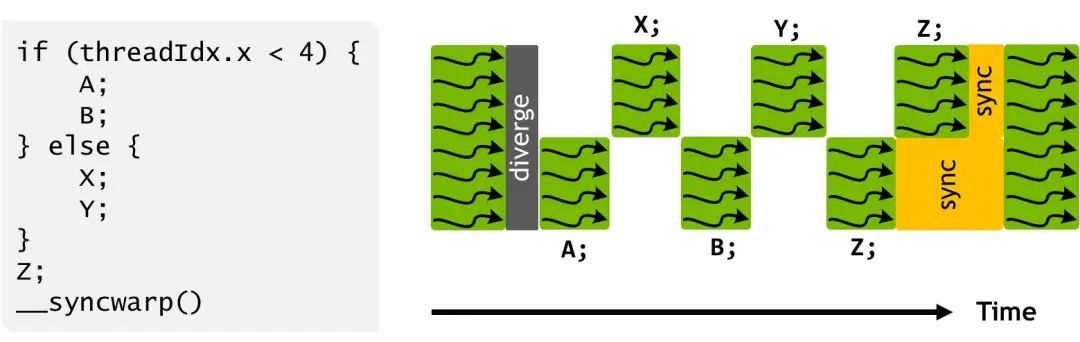

下面我们再来了解下指令流水的 Pipline 是如何组织起来的。

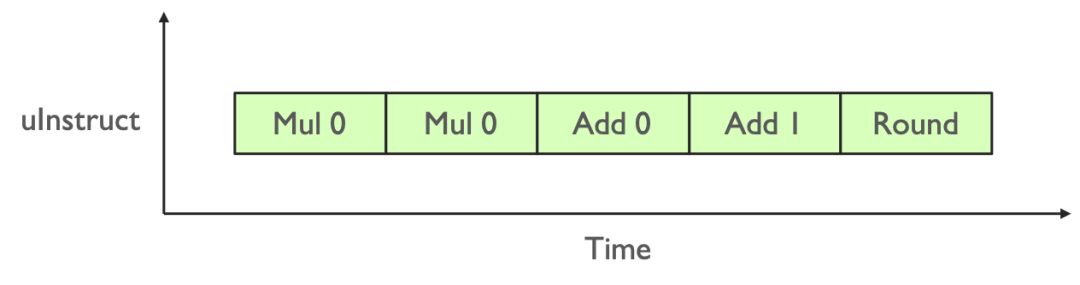

当我们进行一个 Fp32 标量元素乘加操作的指令时,就像下面图所示。

Tensor Core 标量流水线

Tensor Core内乘法运算仅支持Fp16,而存储与加法运算则采用Fp32,巧妙地实现了乘法运算的精简,显著提升计算效率。

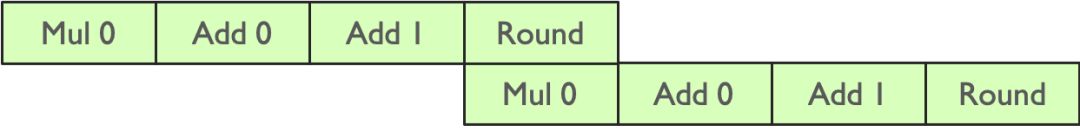

Tensor Core 两个元素流水线

Tensor Core计算时,输出单个元素需A的一行与B的一列相乘,高效实现依赖四条并行Pipeline流水线,确保高效能处理。

Tensor Core 一行 x 一列流水线

图示中,绿色指令流水与黄色流水线共同完成了部分计算。为全面计算所有元素,需高效拼接大量指令流水,确保计算流畅无阻。

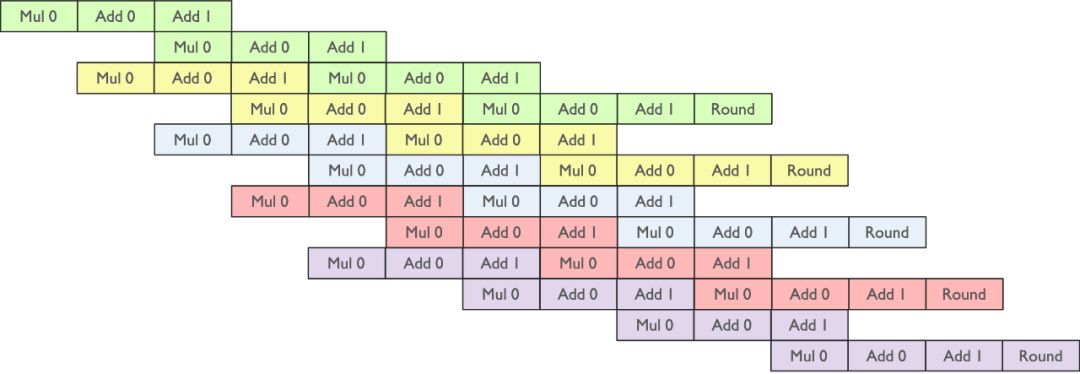

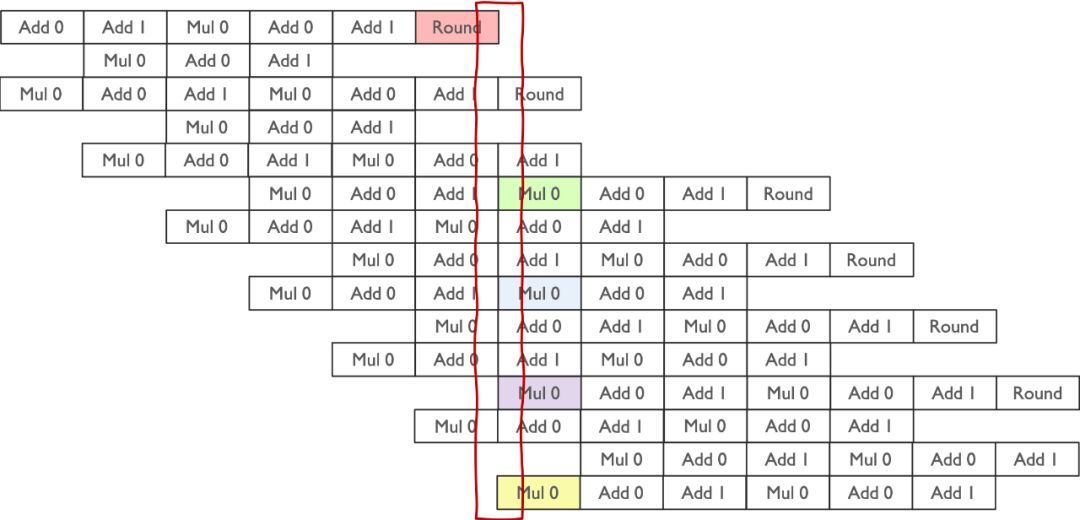

Tensor Core 矩阵流水线

数据在流水线中的读写遵循明确规律:乘法计算时,从存储单元读取两数据;计算完成后,Round阶段将结果写回单元。在特定时刻,流水线涉及四个数据:两个用于计算,两个存储回寄存器。这一流程确保了数据的高效处理与准确存储。

Tensor Core的高效运算得益于精心设计的指令流水线处理。这种设计使数据读取、计算和写入无缝交替,最大化硬件资源利用率,显著提升计算效率。流水线技术不仅加速Tensor Core运算,更为深度学习应用提供强大动力,实现快速、高效的计算体验。

TensorCore 线程执行

在整体 CUDA 软件设计方面,其目的是与 GPU 计算和存储分层结构相匹配。

NVIDIA CUDA定义Tensor Core为通用编程(General Programming)范式,旨在通过CUDA平台最大化Tensor Core的硬件效能。CUDA让开发者能够运用通用编程模型,精准调用Tensor Core功能,实现并行计算的高效运行,从而显著提升计算效率。

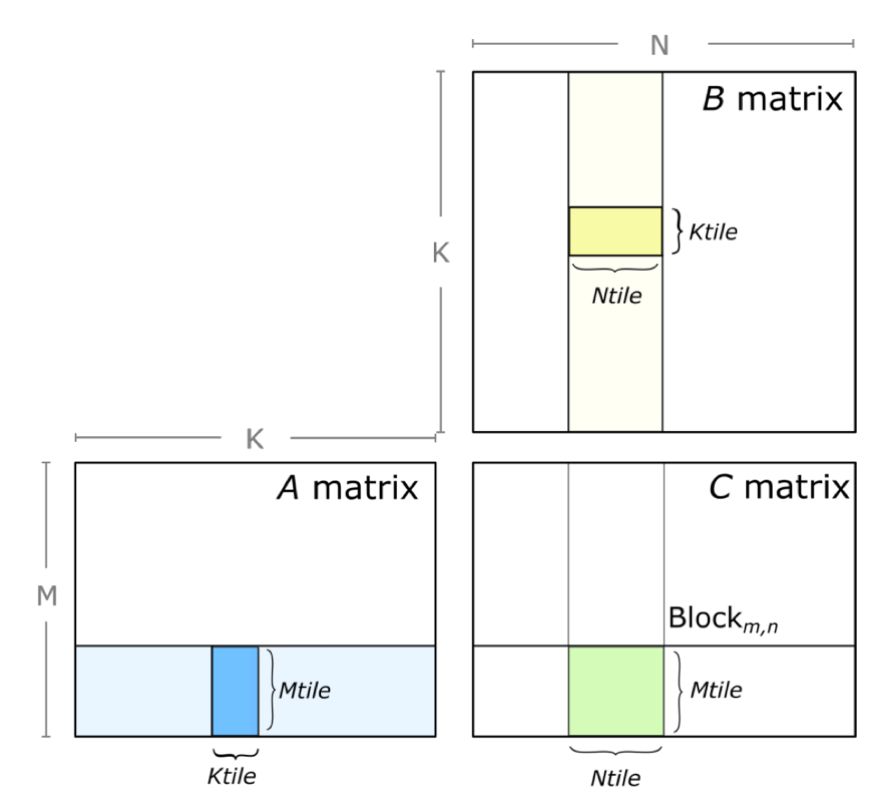

Tensor Core 的计算简化为 C = A * B,但面对大矩阵时,由于 Tensor Core 仅支持4x4的运算,需将矩阵切片并分配到 Thread Block 中。这种分片处理策略确保了大规模矩阵运算的高效执行,充分发挥了 Tensor Core 的计算能力。

在软件层面,我们定义Warp以分配切片矩阵至不同线程束。通过线程并行执行,实现矩阵乘法的高效计算,充分利用Tensor Core的计算潜能。此分块、分配与并行化策略有效释放硬件资源,极大提升计算效率,为深度学习及科学计算等应用带来显著加速效果。

下面我们将详细展开 Tensor Core 是如何完成大的矩阵计算的。

Block-level 矩阵乘

Tensor Core中,GEMM(矩阵乘)每次仅处理小矩阵块。实际操作时,需将矩阵A、B分别切分为小块,以计算出小矩阵C。此过程高效且精准,如图所示。

Block-level 的矩阵乘

for (int mb = O; mb