【cadence virtuoso 实践记录(2)_手动计算设计5管_OTA(有源负载差分对)】

- 1参数指标

- 2计算过程

- 3仿真过程

- 3.1 按照2中计算的W/L搭建原理图

- 3.2仿真结果

- 3.2.1 dc仿真

- 3.2.2 ac仿真

- 3.2.3 3dB 带宽

- 3.2.4 摆率

1参数指标

工艺 SMIC0.18um

工作电压 VDD = 2.5V

摆率 SR ≥ 20V/us

负载电容 C_L = 2 pF

3dB带宽 f 3 d B f_{3dB} f3dB≥ 1MHz

直流增益 |Av| ≥ 40

功耗 P ≤ 0.5mW

共模电压 V_{ICMR} = [ 0.8V , 1.6V ]

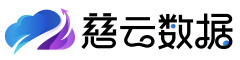

2计算过程

详细过程见手写版

3仿真过程

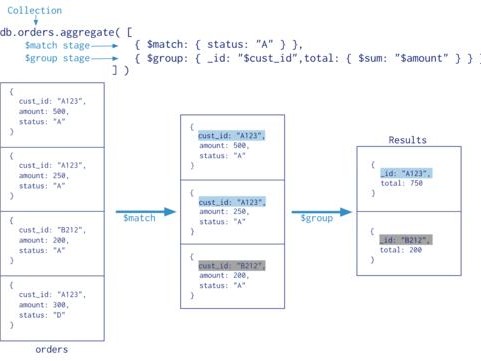

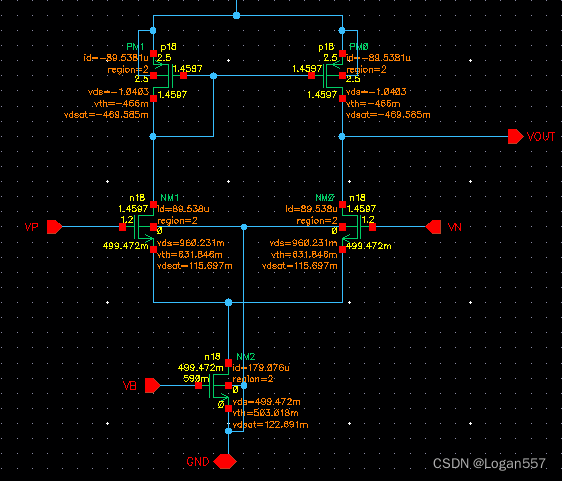

3.1 按照2中计算的W/L搭建原理图

3.2仿真结果

3.2.1 dc仿真

1.设置好2中计算的VCM,VB值

运行直流仿真,检查管子工作状态。

2.一开始尾管的W/L忘了设置,按220/180跑,管子工作在线性区,增加VB到1.5v才饱和,检查后发现问题,调整好管子W/L,后VB给0.59V,即可正常工作。

3.调整管子的静态工作点,还未掌握透彻,需要加强这块的理解。

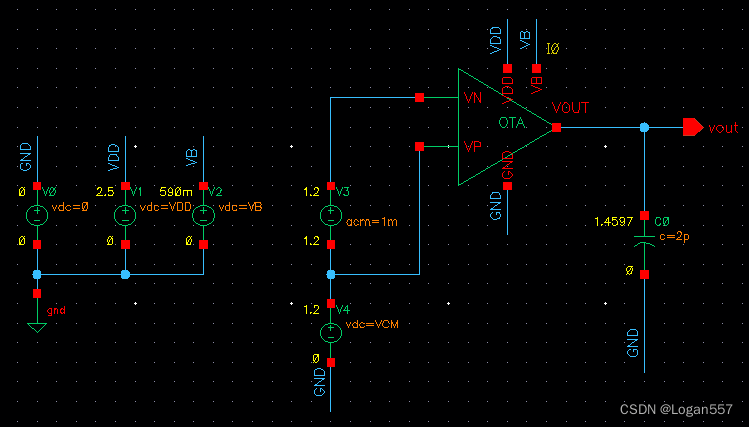

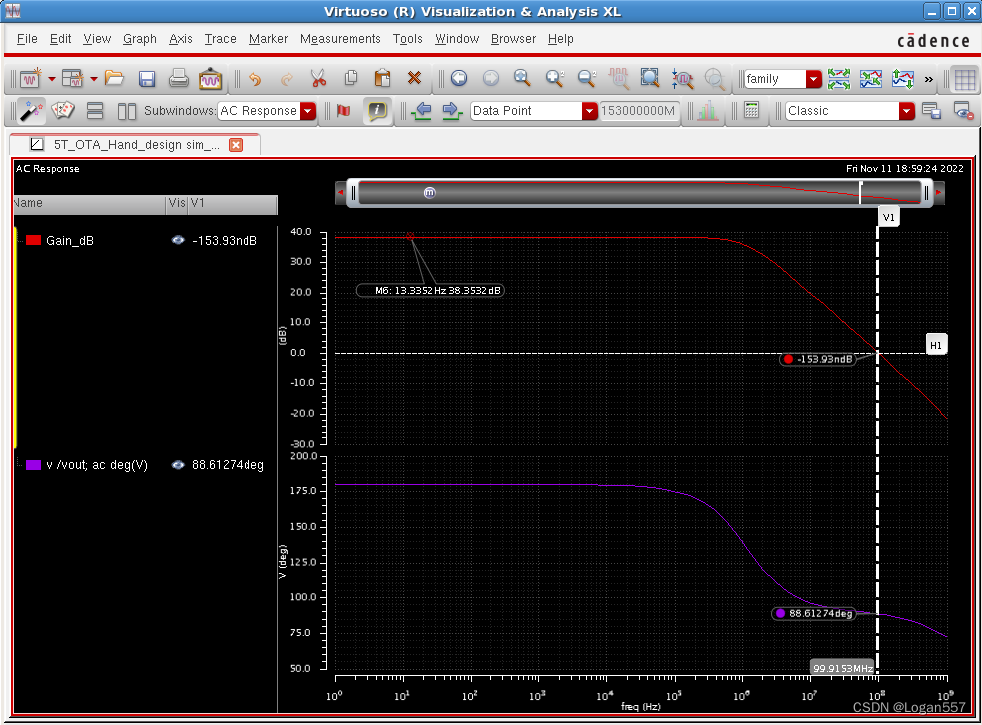

3.2.2 ac仿真

1.输入端加入幅值为0.2V的交流小信号

设置好输出,点击运行,查看增益和相位

图↓testbench

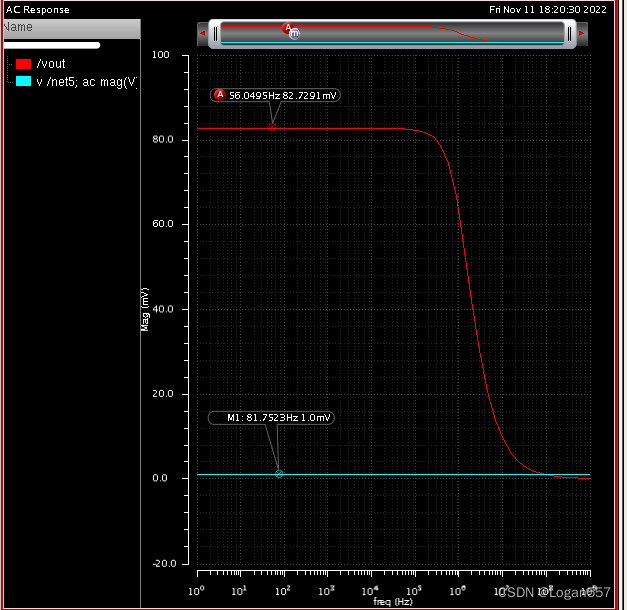

图↓ 增益为82.7

满足指标要求,大于40倍

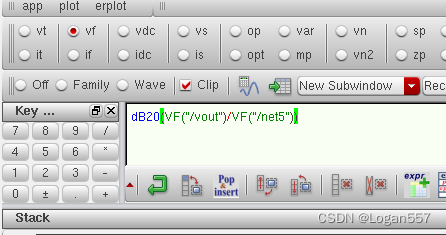

将增益显示为dB

这里注意,因为输入给的是mv,直接用dB20函数计算增益,会出现负值,

20lg(0.0827V) = -21.64dB

这里设置gain_dB的表达式,用输出除以输入,再点击dB20。

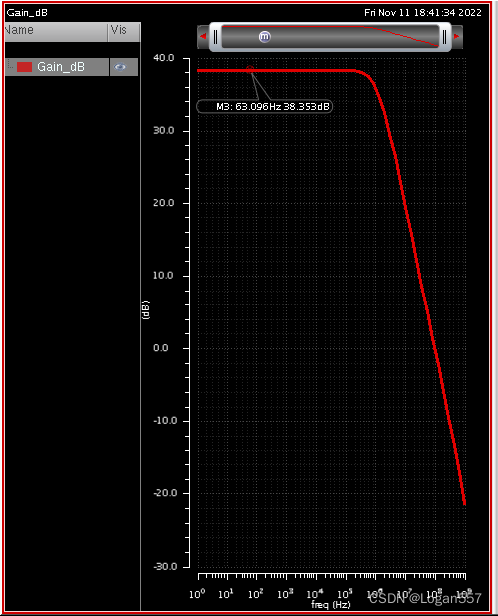

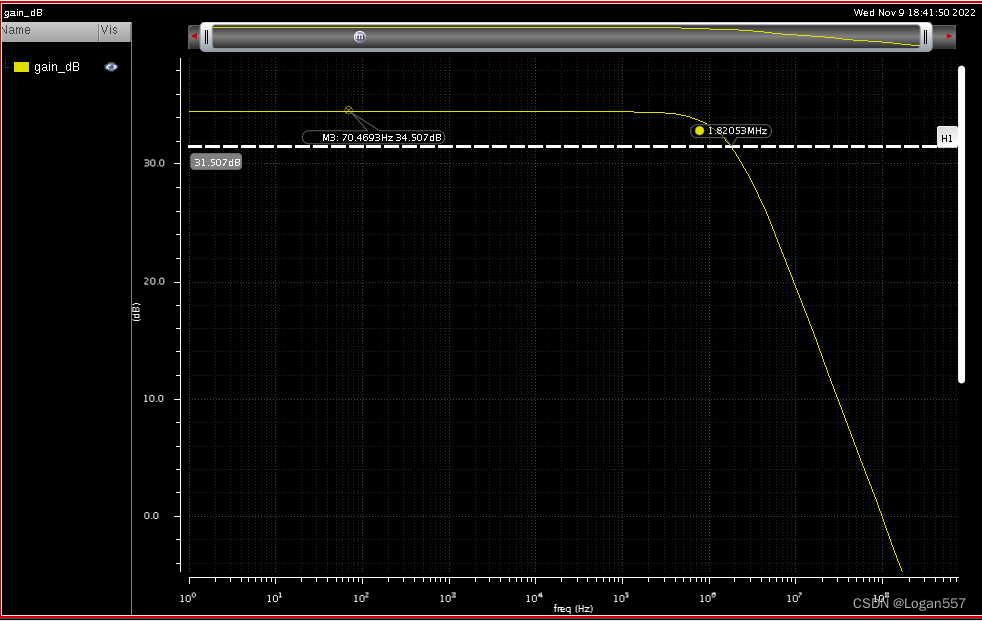

结果显示为38.353dB

增益相位仿真结果

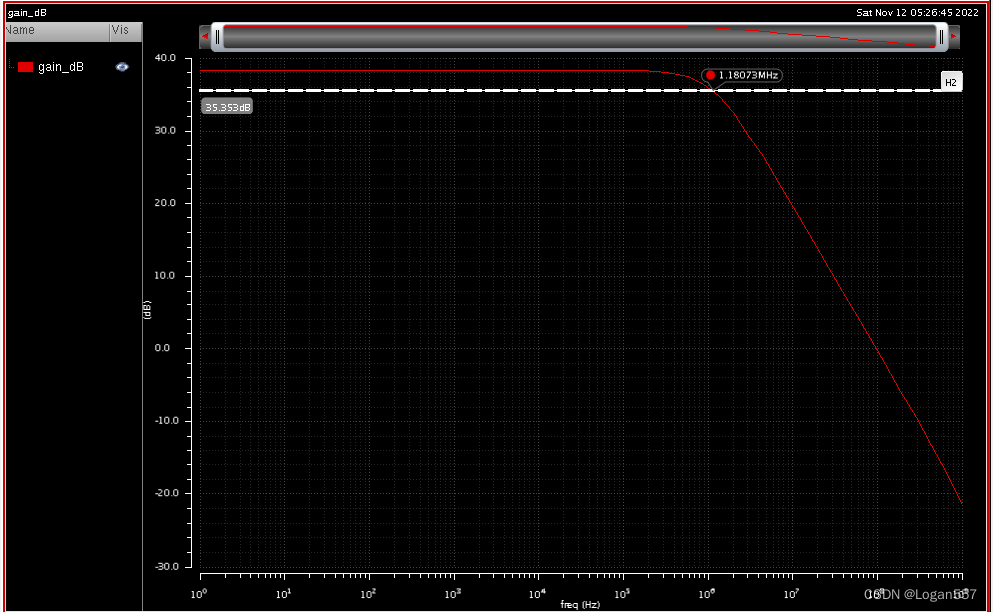

3.2.3 3dB 带宽

按照2中的数据仿真的结果,查看3dB带宽。

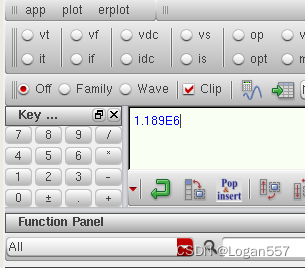

f-3dB=1.18M

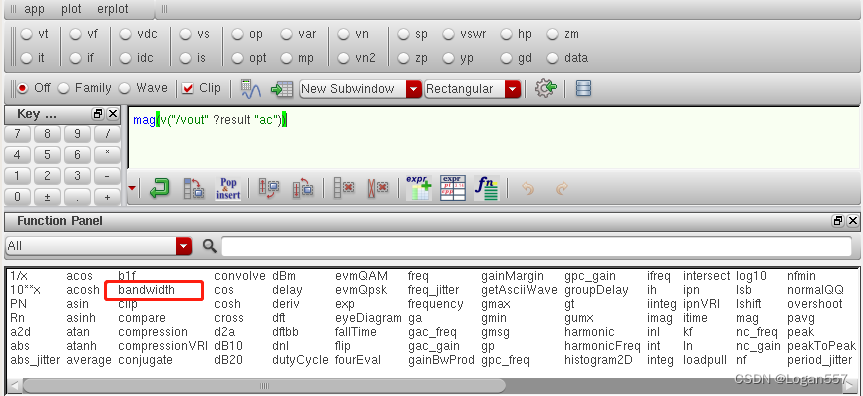

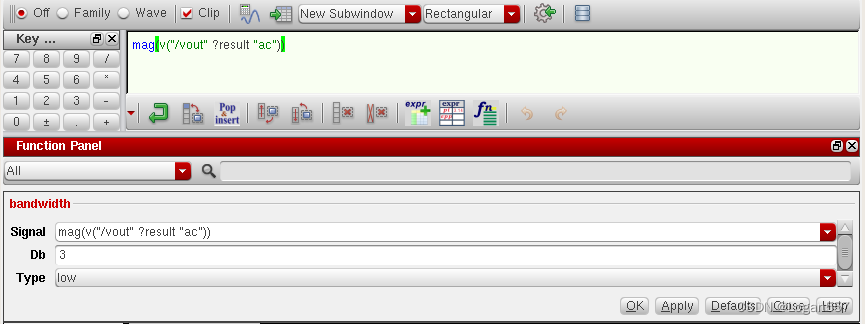

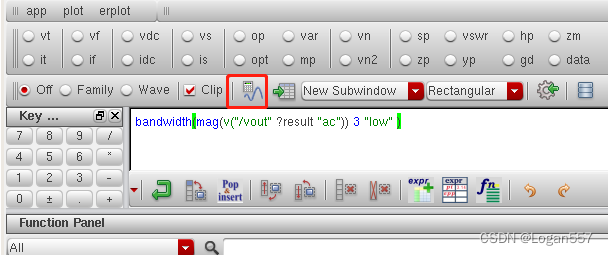

也可以用calculator中的bandwidth函数查看

想要增大3dB带宽,根据公式

f3dB = 1 R o u t C L \frac {1}{R_{out}C_{L}} RoutCL1

R o u t R_{out} Rout = V E L I D \frac {V_{E} L}{I_{D}} IDVEL

那么,减小 R o u t R_{out} Rout → 减小负载管L

得到 f3dB = 1.82MHz

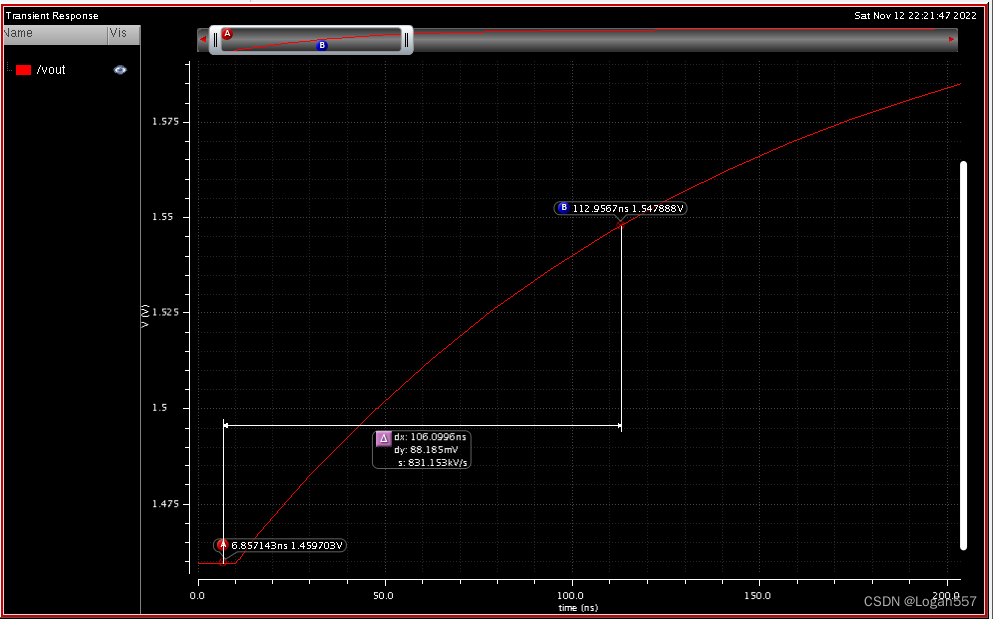

3.2.4 摆率

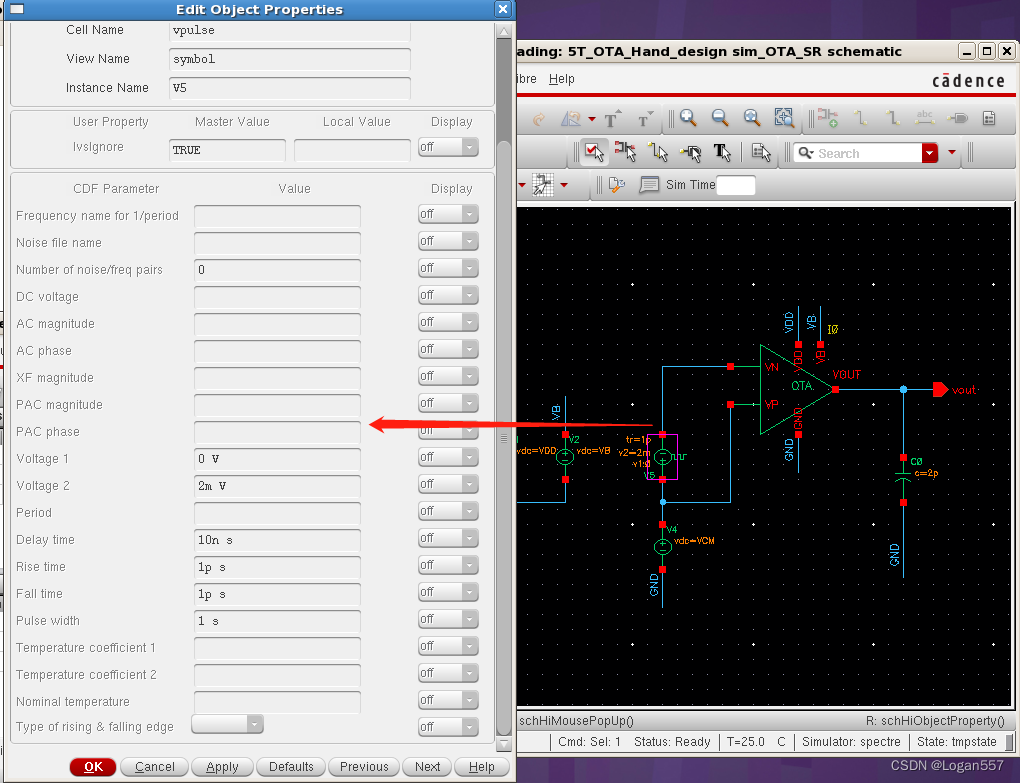

1.将vdc替换成 vpulse,电压设置下

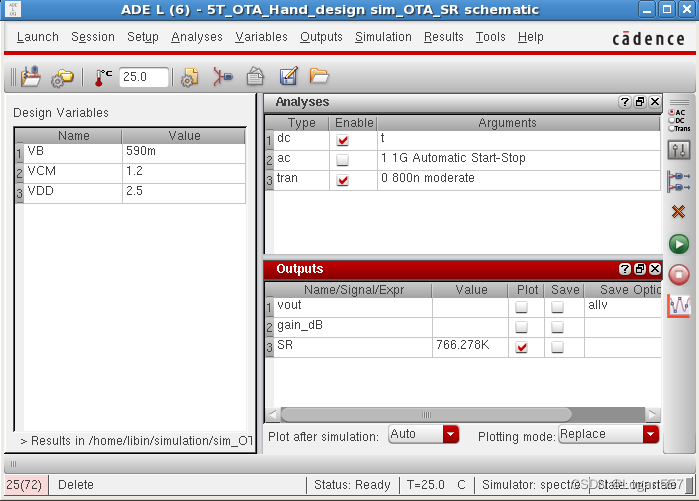

2.设置瞬态仿真窗口

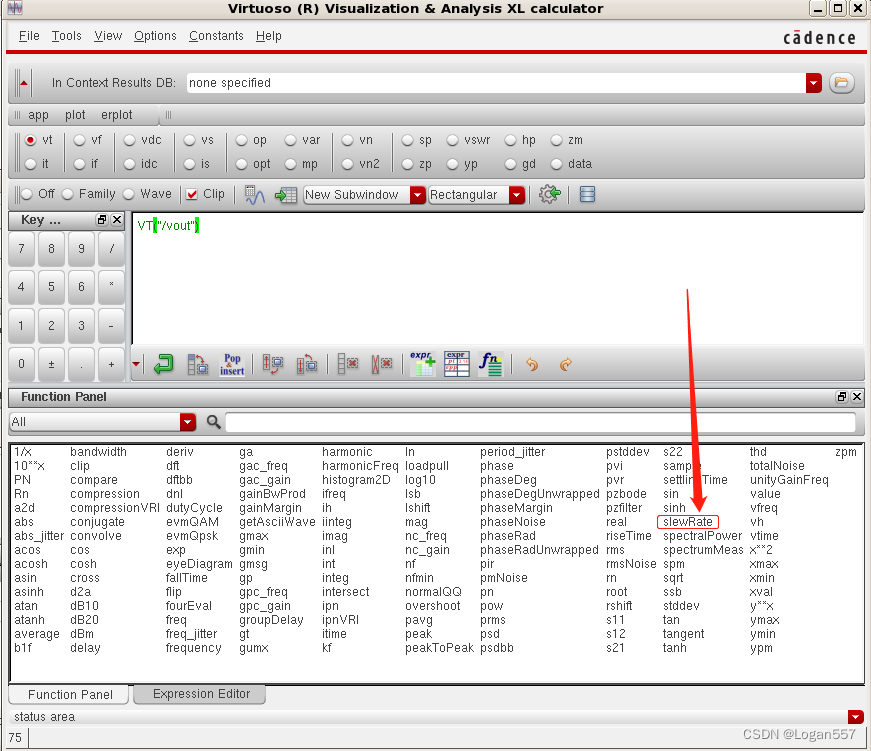

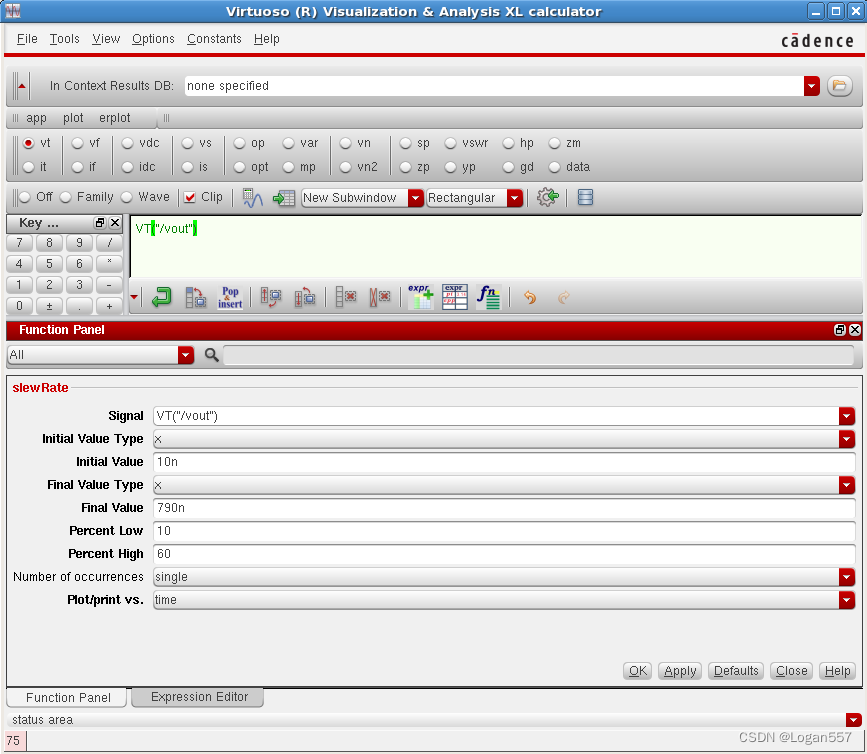

3.设置输出SR

仿真结果显示 SR只有0.776V/μs

未达到设计要求。

改进:

记录:

1.记录有写乱,还没来得及整理

未完待续。。。。