文章目录

- 前言

- 本文主要介绍我在解决12小时计时器问题时的思路,代码以及总结,用于自己复习记录,希望也能帮助到其他人。

- 一.题目

- 二.方法1

- 二.方法2

前言

本文主要介绍我在解决12小时计时器问题时的思路,代码以及总结,用于自己复习记录,希望也能帮助到其他人。

一.题目

HDL bit -12 hour clock题目地址

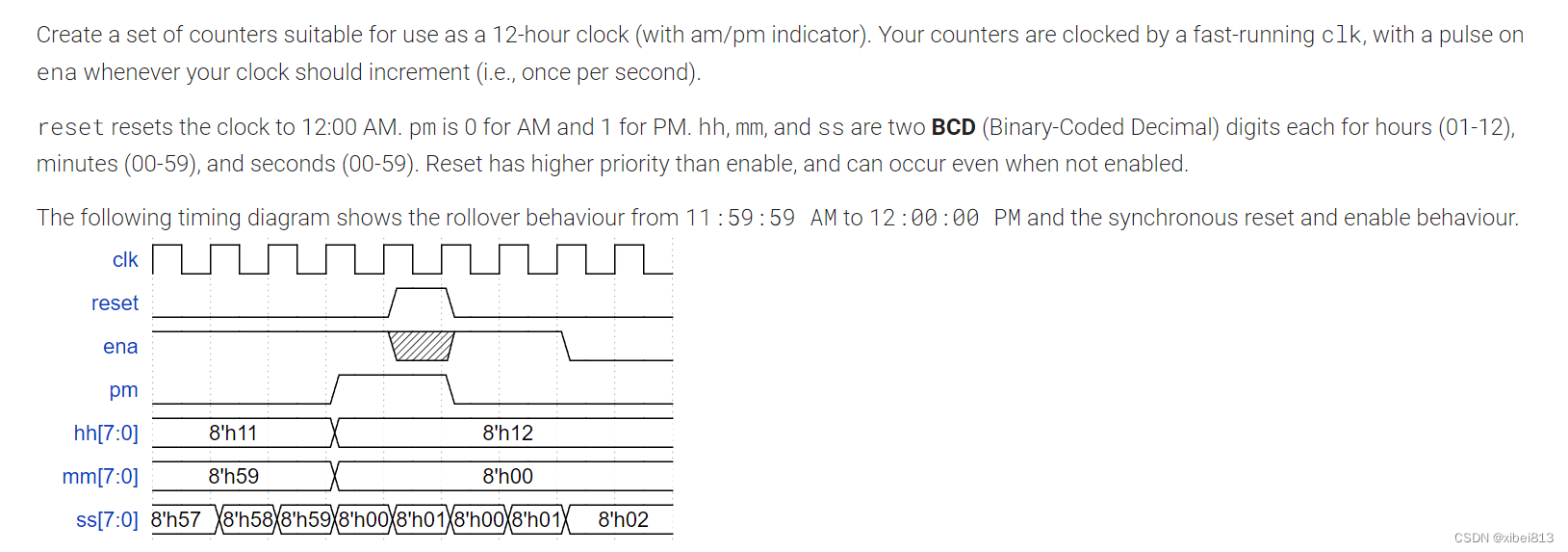

翻译:创建一组适合用作 12 小时制的计数器。计数器由一个快速运行的 clk 计时,每当时钟增加(即每秒一次)时,ena 就会有一个脉冲。

reset 将时钟重置为凌晨 12:00。pm 为 0 表示 AM,1 表示 PM。 hh、mm 和 ss 是两个 BCD(二进制编码十进制)数字,分别表示小时(01-12)、分钟 (00-59) 和秒(00-59)。

重置的优先级高于启用,即使未启用也可能发生。时序图显示了从上午 11:59:59 到下午 12:00:00 的翻转行为以及同步复位和启用行为。

二.方法1

1.完整代码:

module top_module( input clk, input reset, input ena, output pm, output [7:0] hh, output [7:0] mm, output [7:0] ss); reg [3:0] s0; //秒针的个位 reg [3:0] s1; //秒针的十位 //秒计数 always @(posedge clk) begin if(reset) begin s0h1,h0}; assign mm={m1,m0}; assign ss={s1,s0}; assign pm=r_pm; endmodule