5.1 模拟量与数字量概述

模拟量 数字量 模/数转换(A/D, Analog to Digital)数/模转换(D / A, Digital to Analog)

5.2 A/D转换原理及参数指标

在A/D转换器中,由于输入的模拟信号在时间上是连续的,而输出的数字信号是离散的,因此在A/D转换器转换时必须在一系列选定的瞬间(时间坐标轴上一点)对输入的模拟信号采样,然后再将这些采样值转换为数字量。因此一般的A/D转换过程通过采样、量化和编码三个步骤完成的,即首先对输入的模拟电压信号采样,采样结束后进入保持时间,在这段时间将采样的电压量转化为数字量,并按一定的编码形式给出转换结果,然后开始下一次采样。如框图所示:

1. 采样定理

为正确无误地用采样信号vs表示模拟信号vI,必须满足采样定理:

式中, 为采样频率,

为输入信号vI的最高频率分量的频率。

在满足采样定理的条件下,可以用一个低通滤波器将信号vs还原为vI,这个低通滤波器的电压传输系数 在低于

的范围内应保持不变,而在

以前应迅速下降为零。因此,采样定理规定了AD 转换的频率下限。

因此,AD转换器工作时的采样频率至少满足 。采样频率提高以后,留给 AD 转换器每次进行转换的时间也相应缩短了,则要求转换电路必须具备更快的工作速度。因此,不能无限制地提高采样频率,通常取

已经能够满足要求。因为每次把采样电压转换为相应的数字量都需要一定的时间,所以在每次采样以后,必须把采样电压保持一段时间。可见,进行 AD 转换时所用的输入电压,实际上是每次采样结束时的vI值。

有关信号采样相关的理论分析详见《信号与系统》一书第七章内容()

2. 量化与编码

量化 量化误差 用不同的划分方法可以得到不同的量化误差

补充知识:采样电路

(1)电路组成及工作原理:(N沟道MOS管T作为采样开关)

(2)改进电路及工作原理(LE198)

3. 直接A/D转换器

直接A/D转换器能把输入的模拟电压直接转换成输出的数字量而不需要经过中间变量,常用的电路主要有并行比较型和反馈比较型。

(1)并行比较型A/D转换器

三位并行比较型 A/D 转换原理电路如图所示,它由电压比较器、寄存器和代码转换器三部分组成。电压比较器中量化电平的划分采用之前所述的方式,用电阻链把参考电压 VREF分压,得到从1/15VREF~13/15VREF之间7个比较电平,量化单位△=2/15VREF。然后,把这7个比较电平分别接到7个比较器~C,的输入端作为比较基准。同时将要输入的模拟电压同时加到每个比较器的另一个输入端上,与这7个比较基准进行比较。

单片集成并行比较型 AD转换器的产品较多,如AD公司的AD9012(8位)、AD9002(8位)AD9020(10位)等。

并行 AD 转换器特点:

① 由于转换是并行的,其转换时间只受比较器、触发器和编码电路延迟时间限制,因此转换速度快;

② 随着分辨率的提高,元件数目(电压比较器和触发器等)要按几何级数增加。一个n位转换器,所用的比较器个数为 2n-1,如8位的并行 AD 转换器就需要 28-1=255 个比较器。由于位数愈多,电路愈复杂,因此制成分辨率较高的集成并行 AD 转换器是比较困难的;

③ 使用这种含有寄存器的并行 A/D 转换电路时,可以不用附加采样-保持电路,因为比较器和寄存器这两部分也兼有采样-保持功能,这也是该电路的一个优点。

(2)反馈比较型A/D转换器

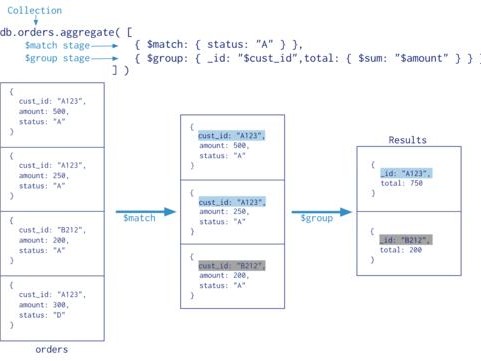

原理:取一个数字量加到 D/A 转换器上,得到一个对应的输出模拟电压,将这个模拟电压和输入的模拟电压信号比较,如果两者不相等,则调整所取的数字量,直到两个模拟电压相等为止,最后所取的这个数字量就是所求的转换结果。

在反馈比较型 A/D 转换器中经常采用的有计数型和逐次比较型两种方案。

(a)计数型 A/D 转换器

下图为计数型 A/D 转换器原理框图。转换电路由比较器C、D/A 转换器、计数器、脉冲源、控制门G 以及输出寄存器等几部分组成:

转换开始前先用复位信号将计数器置0,而且转换控制信号应停留在vL=0的状态,这时门G被封锁,计数器不工作。计数器加给 D/A 转换器的是全0信号,所以 D/A 转换器输出的模拟电压vo=0。如果为正电压信号,转换控制信号vL=1,比较器的输出电压为1,则计数器开始计数工作,DAC输出的逐渐升高直至等于(或大于)vI,比较器的输出电压为0,比较完成D/A的全部位数。

因为在转换过程中计数器中的数字不停地变化,所以不宜将计数器的状态直接作为输出信号,为此在输出端设置了输出寄存器,在每次转换完成以后,用转换控制信号的下降沿将计数器输出的数字置入输出寄存器中,而以寄存器的状态作为最终的输出信号。这个方案的明显问题是转换时间长,当输出为n位二进制数码时,最长的转换时间可达到2n-1倍的时钟信号周期,因此这种方法只能用在对转换速度要求不高的场合。然而由于它的电路非常简单,所以在对转换速度没有严格要求时仍是一种可取的方案。

(b)逐次比较型A/D转换器

逐次逼近型A/D转换器的工作原理可以用如下所示的框图来说明。这种转换器的电路包含比较器C、D/A转换器、寄存器、时钟脉冲源和控制逻辑等5个组成部分。

转换开始前先将寄存器清零,所以加给D/A转换器的数字量也是全0。转换控制信号变为高电平时开始转换,时钟信号首先将寄存器的最高位置成1,使寄存器的输出为100…00。这个数字量被D/A转换器转换成相应的模拟电压vo,并送到比较器与输入信号,进行比较。如果vo>vI,说明数字过大了,则这个1应去掉;如果vo0;x--) for(y=31;y>0;y--); //改进延时为0.5毫秒 } void display(uchar num_bai,uchar num_shi,uchar num_ge) //数码管显示函数 { uint wei; //位选数字 void wedu(uchar dula_num,uchar wela_num); //数码管位选段选函数 for(wei=3;wei